# APPENDIX 6: ACTIVITIES LAUNCHED IN 2025 FOR THE CHIPS FOR EUROPE INITIATIVE PART

Version 6

# **CONTENTS**

|   | ENDIX 6: ACTIVITIES LAUNCHED IN 2025 FOR THE CHIPS FOR COPE INITIATIVE PART1                                                                                                                            |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | ACTIVITIES 2025 CHIPS FOR EUROPE INITIATIVE PART3                                                                                                                                                       |

| 2 | TECHNICAL DESCRIPTION OF THE CALL TOPICS4                                                                                                                                                               |

|   | 2.1 Design Platform4                                                                                                                                                                                    |

|   | 2.1.1 Cloud platform for the European Design Platform7                                                                                                                                                  |

|   | 2.1.2 Set-up and integration of Design Enablement Teams                                                                                                                                                 |

|   | 2.1.3 Support for start-ups and SMEs                                                                                                                                                                    |

|   | 2.1.4 Open-source EDA tools development                                                                                                                                                                 |

|   | 2.1.5 A Pan-European infrastructure for Chips Design Innovation38                                                                                                                                       |

|   | 2.1.6 Low power Edge AI Chips                                                                                                                                                                           |

|   | 2.2 Accelerator for Advanced Strained Silicon on Insulator Substrates48                                                                                                                                 |

|   | 2.3 Quantum Chips54                                                                                                                                                                                     |

|   | 2.3.1 Supporting developing Quantum Chip Technology for superconducting stability Pilot                                                                                                                 |

|   | 2.3.2 Supporting developing Quantum Chip Technology for photonic stability Pilot                                                                                                                        |

|   | 2.3.3 Supporting developing Quantum Chip Technology for semiconducting stability Pilot                                                                                                                  |

|   | 2.3.4 Supporting developing Quantum Chip Technology for diamond-based stability Pilot                                                                                                                   |

|   | 2.3.5 Supporting developing Quantum Chip Technology for neutral atoms stability Pilot                                                                                                                   |

|   | 2.3.6 Supporting developing Quantum Chip Technology for high-quality Trapped Ions Pilot79                                                                                                               |

|   | 2.4 Lab to Fab Accelerators Ecosystem                                                                                                                                                                   |

|   | 2.4.1 Lab to Fab Accelerators for Advanced Packaging and heterogeneous integration                                                                                                                      |

|   | 2.4.2 Lab to Fab Accelerator ecosystem - Coordination and Support Actions. Boosting cooperation for industrial implementation on advanced packaging of chiplets and heterogeneous integration in Europe |

# 1 ACTIVITIES 2025 CHIPS FOR EUROPE INITIATIVE PART

This appendix foresees the launch of the following call topics with an estimated EU expenditure of as below:

| HE ACTIONS                           |                                                                                                                            |                            |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Call Topics                          |                                                                                                                            |                            |

| Topic                                | Description                                                                                                                | Indicative EU budget<br>M€ |

| HORIZON-JU-Chips-2025-<br>CSA        | Pan-European infrastructure for Chips<br>Design Innovation                                                                 | 12                         |

| HORIZON-JU-Chips-2025-<br>IA-EDA     | Open-source EDA tools development                                                                                          | 20                         |

|                                      | Other actions not subject to calls for proposals                                                                           |                            |

| HORIZON-JU-Chips-2025-<br>RIA-SUP    | Support for start-ups and SMEs                                                                                             | 220                        |

| HORIZON-JU-Chips-2025-<br>QAC1-1-SGA | Supporting developing Quantum Chip Technology for superconducting stability Pilot                                          | 25                         |

| HORIZON-JU-Chips-2025-<br>QAC1-2-SGA | Supporting developing Quantum Chip<br>Technology for photonic stability Pilot                                              | 25                         |

| HORIZON-JU-Chips-2025-<br>QAC1-3-SGA | Supporting developing Quantum Chip<br>Technology for semiconducting stability<br>Pilot                                     | 25                         |

| HORIZON-JU-Chips-2025-<br>QAC1-4-SGA | Supporting developing Quantum Chip<br>Technology for diamond-based stability Pilot                                         | 25                         |

| HORIZON-JU-Chips-2025-<br>QAC1-5-SGA | Supporting developing Quantum Chip Technology for neutral atoms stability Pilot                                            | 25                         |

| HORIZON-JU-Chips-2025-<br>QAC2-SGA   | Supporting developing Quantum Chip Technology for high-quality Trapped Ions Pilot                                          | 25                         |

|                                      | DEP ACTIONS                                                                                                                |                            |

| Topic                                | Call Topics  Description                                                                                                   | Indicative EU budget<br>M€ |

| DIGITAL-JU-Chips-2025-<br>CSA-DET    | Set-up and integration of Design Enablement<br>Teams                                                                       | 5                          |

| DIGITAL-Chips-2025-1-<br>IA-LEAI     | Low-power Edge AI Chips                                                                                                    | 20                         |

| DIGITAL-JU-Chips-2025-<br>SG-SSOI    | Accelerator for Advanced Strained Silicon on Insulator Substrates                                                          | 30                         |

| DIGITAL-JU-Chips-2025-<br>SG-LFA     | Lab to Fab Accelerators for Advanced Packaging and heterogeneous integration                                               | 50                         |

| DIGITAL-JU-Chips-2025-<br>CSA-LFA    | Lab to Fab Accelerator ecosystem - Coordination and Support Actions. Boosting cooperation for industrial implementation on | 2                          |

|                  | advanced packaging of chiplets and               |                      |

|------------------|--------------------------------------------------|----------------------|

|                  | heterogeneous integration in Europe              |                      |

|                  | Other actions not subject to calls for proposals |                      |

| Topic            | Description                                      | Indicative EU budget |

|                  |                                                  | M€                   |

| Call for tenders | Cloud platform for the European Design           | 15                   |

|                  | Platform                                         | 15                   |

| TOTAL            |                                                  | 424                  |

## 2 TECHNICAL DESCRIPTION OF THE CALL TOPICS

In addition to the application of Article 22(5) of the Horizon Europe Regulation¹ (HE) to the relevant topics of the Chips JU's work programme, in line with Article 23 of the Single Basic Act, in order to ensure a coherent application of Article 22(5) HE, as well as Union legislation and guidance application in similar topics in the work programme of the Chips JU, eligibility of participants in a proposal submitted to a Call for Proposals for any of the topics in this work programme will take into account any application of Article 22(5) of HE triggered for topics from other HE Work Programmes (including the Chips JU's work programme) for calls for proposals with similar scope. This may be of particular relevance to proposals submitted to bottom-up RIA/IA topics, i.c. topics HORIZON-JU-Chips-2025-IA and HORIZON-Chips-2025-RIA, where despite the fact that Article 22(5) HE might already be used, stricter conditions may apply in case those proposals address areas covered under other HE work programme topics with a stricter application of Article 22(5) HE.

## 2.1 Design Platform

Semiconductor circuit design involves the development of integrated circuits (ICs) and system-on-chips (SoCs) by defining the functionalities and specifications of chips, capturing a significant share of the value within the semiconductor supply chain. The industry is increasingly shifting towards more complex, application-specific, and highly integrated semiconductors, making state-of-the-art design essential for competitiveness and differentiation across various applications. In this evolving landscape, fabless companies are uniquely positioned to lead technological innovation and address the demands of diverse applications, further solidifying their critical role and driving growth within the semiconductor sector.

The Chips Act underscores the strategic importance of fostering chip design growth in Europe to enhance the competitiveness of the Union's semiconductor industry. Pillar I of the Chips Act, the Chips for Europe Initiative, outlines an ambitious plan to strengthen the Union's resilience in semiconductor technologies, including promoting the growth of fabless companies focused on leading-edge technologies. This is especially pertinent given that the European

<sup>&</sup>lt;sup>1</sup> Regulation (EU) 2021/695 of the European Parliament and of the Council of 28 April 2021 establishing Horizon Europe – the Framework Programme for Research and Innovation, laying down its rules for participation and dissemination

share of global fabless semiconductor companies' revenues has shrunk to critically low levels, highlighting the urgent need for strategic initiatives to bolster this sector and enhance Europe's competitiveness. A critical mass of fabless companies is also key to generate further demand that would justify increased investment in semiconductor manufacturing capacity in Europe.

Recognising the Union's limited fabless capacity, and the significant barriers to entry in chip design, the Design Platform focuses on nurturing emerging companies in the sector. The Design Platform is at the heart of the Chips for Europe Initiative and is envisaged as a key instrument to foster the development of a strong design ecosystem in the Union by creating a pipeline of highly innovative European fabless companies, focusing particularly on the growth of start-ups and SMEs.

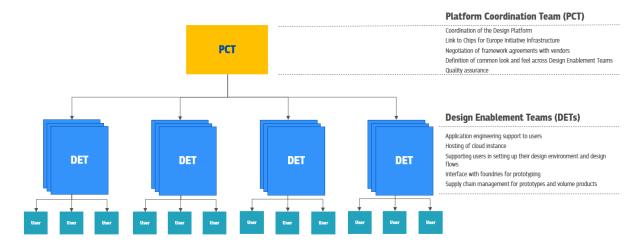

In 2024, the Chips Joint Undertaking launched a call for the selection of a Platform Coordination Team (PCT). The selected PCT should assist the Chips JU in defining the technical specifications of a cloud service for the platform to be procured by the Chips JU through a dedicated Call for Tenders. This cloud infrastructure should incorporate all the services necessary for the efficient implementation of the Design Platform including repositories, a user authentication service, license usage monitoring and any relevant *Infrastructure as Code* to be deployed at the various Design Enablement Teams (DETs).

The PCT will be complemented by a number of DETs that should set up a cloud-based environment for users designing on the platform, support them in their design cycle, and facilitate access of users to foundry services. Furthermore, the DETs should be responsible for providing access to foundry services. In fact, it should be a pre-requisite that for an entity to become a DET, it must act as, or be linked to, a foundry aggregator.<sup>2</sup>

These DETs may be design houses and RTOs with the necessary expertise and experience in providing such services. They can be spread geographically but may also have different sectoral (e.g. defence) or technological (e.g. digital, analogue, photonics) focus. The selection of DETs should take place via an open and inclusive process, based on fulfilment of certain technical and security requirements. Any design service provider fulfilling such requirements may apply for integration into the platform. The PCT should provide the set of requirements that DETs must fulfil in order to apply for integration in the cloud-based platform.

To this end this work programme includes the following topics:

- Cloud platform for the European Design Platform

- Set-up and integration of Design Enablement Teams

- Support to start-ups and SMEs.

- Open-source EDA tools development

- Low power Edge AI Chips

-

<sup>&</sup>lt;sup>2</sup> A foundry aggregator is an industry standard term used for companies that act as an intermediary between fabless semiconductor companies (clients) and semiconductor foundries (manufacturers). Typically, only large enterprises directly engage with foundries.

## 2.1.1 Cloud platform for the European Design Platform

| Type of Action                             | Call for tenders |

|--------------------------------------------|------------------|

| Indicative EU budget (from the DEP budget) | 15 M€            |

| Mode                                       | EU funding only  |

### 2.1.1.1 Context

<u>Note:</u> A formal call for tenders will be published over the course of 2025. The current text should not be considered as a formal Call for Tenders within the context of a procurement procedure. Information listed here is purely indicative.

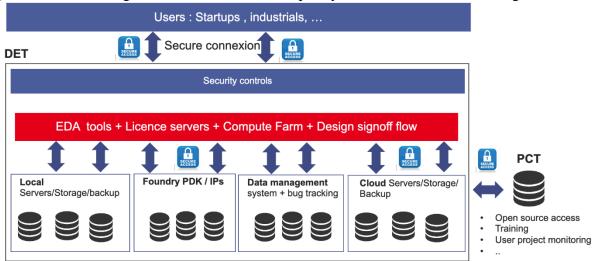

Chip design is a key weakness in Europe's semiconductor ecosystem. Fabless revenues in Europe represent less than 1% of global revenues. Recognising the importance of this sector to the value chain, Pillar 1 of the Chips Act, the Chips for Europe Initiative foresees a design platform to enable start-ups and SMEs to venture in design. The Design Platform is foreseen to serve as a hub of services and resources for its users and to this end the Chips Joint Undertaking should procure a cloud infrastructure to enable the implementation of said platform. The cloud infrastructure should include both the underlying cloud service as well as any related development of custom software.

## 2.1.1.2 Scope

The central cloud infrastructure should host the IP, PDKs and open-source EDA tools as well as training services. This should be accompanied by a user authentication service. Interested parties should therefore be responsible for the provisioning and management of a secure and scalable cloud infrastructure capable of hosting these key elements of the Design Platform and its associated services. The selected service provider should be responsible for the setting up and maintenance of this service for 4 years.

This should be accompanied by a vendor-neutral software solution for automated infrastructure configuration, referred to here as Infrastructure as Code (IaC), to be deployed at the various Design Enablement Teams as part of a federated cloud infrastructure for the Design Platform. The purpose of this IaC should be to:

- Standardise deployment: The IaC should enable the Platform Coordination Team (PCT) to define and enforce a standardised configuration for DET cloud environments through code, ensuring that all DETs adhere to the same security protocols, service level agreements, and access controls. This would ensure a more consistent and reliable user experience across different DETs.

- **Automate provisioning**: The IaC related tools should be used to automate the provisioning of cloud resources for DETs. This would simplify the process of setting

- up and scaling design environments, reducing the potential for manual errors and freeing up DET resources to focus on user support and other value-added services.

- Ensure version control and reproducibility: Through the IaC, the PCT should be able to leverage version control systems to track changes and ensure that environments can be easily reproduced. This should be crucial for maintaining consistency over time, simplifying troubleshooting, and facilitating the rollback of changes if needed.

- Enhance security and compliance: The IaC can help enforce security best practices by automating security configurations and checks. This could be particularly relevant for the DP, given the sensitive nature of design data and IP. By codifying security policies, the PCT could help ensure a more secure and compliant design environment for all users.

## 2.1.1.3 Expected outcomes.

The requested cloud services should primarily contain the following elements:

- A repository populated with an extensive portfolio of open-source and proprietary 'design assets' to facilitate and enhance the design process for users, such as intellectual property (IP) blocks, design templates, fast adoption kits, process design kits (PDKs) from pilot lines and open foundries, open-source design tools, as well as reusable open-access design elements from previous EU-funded projects.

- Any suitable features, such as user authentication and license usage monitoring, that are deemed useful for the management of the overall initiative and the various DETs in the Design Platform.

- Templates of virtual machines or containers containing all the software components and configuration required to operate a given electronic design software, and that can be easily deployed on the cloud instances operated by the DETs.

The selected tender should also be responsible for the running and maintenance of this service for 4 years.

The latter point should be complemented by the development of an *Infrastructure as Code* (IaC) framework that supports a variety of cloud vendors. Work related to the development and management of the IaC should be coordinated by the PCT and deployed across various DETs. The purpose of this IaC is to facilitate cloud deployment at the various DETs, ensure baseline security standards, and provide a consistent experience across different DETs. Where possible, cloud vendor-agnostic resources should be used, accompanied by vendor-specific configurations where necessary. The service of developing the IaC should also be procured by the Chips JU with the technical assistance of the PCT.

All resources involved in this development should be based in the EU, including the location of the cloud-related data centres.

Further details will be presented in the Call for Tenders when published.

## 2.1.2 Set-up and integration of Design Enablement Teams

Topic: DIGITAL-JU-Chips-2025-CSA-DET

| Type of Action                       | CSA                                                                                                                                                                                                                                   |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Indicative EU budget                 | 5 M€                                                                                                                                                                                                                                  |

| Expected EU contribution per project | The JU estimates that an EU contribution of around EUR 0.5 million would allow these outcomes to be addressed appropriately. Nonetheless, this does not preclude submission and selection of a proposal requesting different amounts. |

| Mode                                 | EU funding only  One stage Call with submission of Full Proposal (FPP)                                                                                                                                                                |

| Call launch date                     | 04th of June 2025                                                                                                                                                                                                                     |

| Deadline FPP Phase                   | 30th of July 2025                                                                                                                                                                                                                     |

#### 2.1.2.1 Context

Semiconductor circuit design is the process of creating integrated circuits (ICs) by defining the functionalities and characteristics of chips, capturing a substantial portion of the added value within the semiconductor value chain. The trend is moving towards more complex, application-specific, highly integrated semiconductors, making cutting-edge design crucial for competitiveness and differentiation in a wide range of applications. In this context, fabless semiconductor companies are well-positioned to drive technological advancements and meet the needs of diverse applications, reinforcing their pivotal role and growth in the semiconductor industry.

The Chips Act underscores the strategic importance of fostering chip design growth in Europe to enhance the competitiveness of the Union's semiconductor industry. Pillar I of the Chips Act, the Chips for Europe Initiative, outlines an ambitious plan to strengthen the Union's resilience in semiconductor technologies, including promoting the growth of fabless semiconductor companies. This is especially pertinent given that the European share of global fabless semiconductor companies' revenues has shrunk to critically low levels, highlighting the urgent need for strategic initiatives to bolster this sector and enhance Europe's competitiveness. A critical mass of fabless companies is also key to generate further demand that would justify increased investment in semiconductor manufacturing capacity in Europe.

The Design Platform is at the heart of the Chips for Europe Initiative. It is envisaged as a key instrument for fostering the development of a strong semiconductor design ecosystem in the Union, by supporting the growth of highly innovative European fabless start-ups and SMEs. Considering the Union's limited fabless capacity, and the significant barriers to entry

in chip design, the Design Platform will focus on nurturing emerging companies in the sector by enabling their access to a comprehensive chip design ecosystem from early stages up to tape-out.

This ecosystem includes a series of Electronic Design Automation (EDA) tools, Intellectual Property (IP) blocks and Process/Assembly Design Kits (P/ADKs) including standard cell libraries. This is coupled with either on-premise or cloud-based computing resources. Furthermore, access to foundries, packaging and test facilities is crucial. Each of these elements requires a separate acquisition process for the designer, often involving very significant costs and its own complex procedures.

## 2.1.2.2 Scope

The Design Platform should act as a hub of services to support European companies engaged in chip design. The Design Platform is implemented via two main classes of entities:

- The **Platform Coordination Team (PCT)** which coordinates the Design Platform, establishes framework agreements with EDA/IP suppliers and provides access to a central cloud service encompassing a marketplace with open source or proprietary IPs/EDA tools/PDKs and trainings amongst other resources. The PCT also provides DETs with Infrastructure as Code to ease the deployment of cloud instances. Through internal expertise and, where necessary, sub-contracting, the PCT and DETs collaborate to design and implement the overarching technical implementation of the platform and design interfaces with the distributed services, as well as ensuring the overall neutrality of the platform

- The **Design Enablement Teams** (**DETs**) each of which is in charge managing a distributed cloud instance and providing dedicated application engineering support to users from setting up their design environment and design flows up to tape-out. A DET can be a single entity, or a consortium of entities selected among providers of chips design support services, such as design houses, RTOs or other entities currently providing design enablement services on a commercial basis. DETs should be selected based on their technology expertise (e.g., digital, analogue, mixed-signal, photonics, etc.), ability to offer support across the end-to-end design flow, access to fabrication services (foundries, packaging, test services) and a proven track record of delivering high quality services to users, amongst other characteristics.

A call (*DIGITAL-Chips-2024-CSA-CDP-1*) to select a Platform Coordination Team was launched in July 2024. The scope of the current call is to select a number of Design Enablement Teams.

## 2.1.2.3 Expected outcomes.

The core functions of DETs include, but are not limited to:

- 1. **Deployment of Electronic Design Automation (EDA) tools on the cloud**: DETs will manage secured cloud instances facilitating access to essential design tools and simulation environments. To this end, DETs may contract with a cloud provider of their choice to setup this infrastructure.<sup>3</sup> It is expected that prospective DETs demonstrate experience in commercial designs using tools from established EDA vendors.

- 2. **Design flow support and customisation**: DETs will assist users in setting up and customising design environments and flows, ensuring smooth progression from initial setup to tape-out.

- 3. **Application engineering**: DETs will offer dedicated application engineering support, addressing specific user needs and challenges throughout the development process.

- 4. Access to Process Design Kits (PDKs): DETs will provide users with access to the necessary PDKs and ADKs for their design projects. Each DET must have legal authorisation to use and/or provide its users access to PDKs/ADKs of at least one semiconductor foundry.

- 5. **Design expertise**: DETs will provide users with access to the necessary design expertise for their design projects, directly via the DET's resources and/or through partnerships with third parties.

<sup>&</sup>lt;sup>3</sup> Cloud services utilised by the DET shall comply with robust cybersecurity security requirements such as the CEN/TS 18026:2024 standard or equivalent.

6. **Prototyping and fabrication services**: DETs will facilitate prototyping and fabrication services including packaging and testing through partnerships with leading foundries or aggregators, the Chips for Europe Initiative pilot lines or other relevant pilot lines. Each DET must have already established direct or indirect relationships with at least one semiconductor foundry, enabling efficient communication and ensuring technology advice and support to its users.

Overall, it is expected that each DET should manage a cloud instance offering dedicated application engineering support to users, from setting up their design environment and design flows to tape-out. The level of security of that cloud instance should be commensurate to the categories of users and applications that are expected to be running on this instance. The DET will maintain a cloud-based connection to the PCT's central cloud to manage user access, extend its capacity with additional resources (open-source IPs, EDA Tools, PDK...) and deliver periodic monitoring data to increase the quality of service of the Design Platform.

Figure 2 - High-level illustration of DET cloud-instance

DETs will be selected based on the extent of their technology expertise (e.g. digital, analogue, mixed-signal, photonics, etc.), ability to offer support across the end-to-end design flow, including PPA optimisation, access to fabrication services, and a proven track record of delivering high-quality services to users, among other characteristics.

These DETs could be public or private organisations that offer custom design support services, such as ASIC design houses and RTOs, with a demonstrated track record of expertise and experience in providing such services. Overall, the DETs should cover a wide variety of semiconductor technologies and can have different sectoral focuses (e.g. automotive, defence).

The only eligible costs for beneficiaries are those **directly related to the set-up and integration of DET's cloud services into the design platform**. This integration will be executed through a shared customer portal and the deployment of an Infrastructure as Code solution developed specifically for the Design Platform to ensure a consistent user experience.

The PCT will give access to these solutions to the designated DETs, for instance through an API. Any costs related to the infrastructure of the cloud provider of choice or through onpremise infrastructure, are considered to be part of the standard business proposition and competitive offering of the DET; as such, these costs are not considered eligible.

During the initial phase, the central cloud infrastructure of the design platform is likely to be still under development and thus not yet available for integration with the DET cloud service. Nevertheless, a preliminary trial phase of the design platform involving a limited set of test users may commence, and the selected DETs should be prepared to provide support and enablement services directly to such users from their own infrastructure, until the central platform becomes available for full service integration.

The selection process will ensure that collectively the selected DETs cover a broad range of technologies (CMOS and more than Moore technologies) and design topologies (analog, digital, mixed-signal etc.), for various applications (e.g. automotive, aeronautics, consumer, health etc). Preference will be given to DET candidates that address in their proposal at least one of the following technologies: CMOS bulk, FDSOI, finFET or Photonics. Strategies to collaborate with the Chips for Europe Initiative pilot lines are highly valued.

Proposals should provide a detailed explanation of the cloud services to be used by the DET, including their performance specifications and cybersecurity measures. Cloud services utilised by the DET should comply with robust cybersecurity requirements.<sup>4</sup>

DETs should also demonstrate capacity to effectively serve users across all the participating states of the Chips JU.

Finally, DET proposals which include members of the PCT consortium should clearly demonstrate effective measures to establish and maintain a strict separation between the two entities, including separate personnel and controlled communication channels, in order to ensure the full neutrality and independence of the PCT.

## 2.1.2.4 Admissibility

Admissibility conditions are described in Annex 2 "General DIGITAL EUROPE PROGRAMME conditions" of the WP General Annexes.

## Regarding page limits:

• The page limit for the chapter RELEVANCE is 10 pages.

- The page limit for the chapter IMPLEMENTATION + chapter 4 of the template for the proposal (Part B) is 40 pages.

- The page limit for the chapter IMPACT is 10 pages.

-

<sup>&</sup>lt;sup>4</sup> Such as the CEN/TS 18026:2024 standard or equivalent.

## 2.1.2.5 Eligibility

Eligibility conditions are described in Annex 2 of the WP General Annexes.

The following exceptions apply:

- Subject to participation restrictions for the protection of European digital infrastructures, communication and information systems, and related supply chains, as described in Annex 4 of the WP General Annexes.

- Legal entities that are established in the Union or EEA countries but are controlled from third countries may only participate on the condition that they guarantee the protection of the essential security interests of the Union and the Member States and that they ensure the protection of classified documents information. Where applicable, security guarantees need to be provided after proposal selection.

## 2.1.2.6 Financial and operational capacity and exclusion

Please refer to Annex 2 "General DIGITAL EUROPE PROGRAMME conditions" of the WP General Annexes.

#### 2.1.2.7 Evaluation procedure

Please refer to the Governing Board Decision on the evaluation and selection procedures related to the calls launched by the Chips JU (GB 2024.71).

For the priority order of proposals with the same score, please refer to Annex 2 "General DIGITAL EUROPE PROGRAMME conditions" of the WP General Annexes.

## 2.1.2.8 Award criteria.

Please refer to Annex 2 "General DIGITAL EUROPE PROGRAMME conditions" of the WP General Annexes.

Specific rules may apply regarding the eligibility to national funding.

For more details, please refer to the Governing Board Decision on the evaluation and selection procedures related to the calls launched by the Chips JU (GB 2024.71).

#### 2.1.2.9 Scores

The scores will be given with a resolution of one decimal.

| Criteria       | Range | Weight (**) | Threshold (*) |

|----------------|-------|-------------|---------------|

| Relevance      | 0-5   | 1           | 3             |

| Implementation | 0-5   | 1           | 3             |

| Impact | 0-5  | 1 | 3  |

|--------|------|---|----|

| Total  | 0-15 |   | 10 |

<sup>(\*)</sup> threshold applies to unweighted score.

# 2.1.2.10 Reimbursement rate for establishing the EU contribution.

Reimbursement rates as percentages of the eligible cost according to DIGITAL.

| Type of beneficiary                    | Maximum EU Contribution as % of eligible costs according to DIGITAL |

|----------------------------------------|---------------------------------------------------------------------|

| For profit organization but not an SME | 100%                                                                |

| SME (for profit SME)                   | 100 %                                                               |

| University/Other (not for profit)      | 100 %                                                               |

<sup>(\*\*)</sup> the weight is only used to establish the ranking of the proposals.

## 2.1.3 Support for start-ups and SMEs

Topic: HORIZON-JU-Chips-2025-IA-SUP

## Support to start-ups and SMEs making use of the Design Platform

| Specific conditions                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Type of Action                                        | Grant to identified beneficiary according to Financial Regulation Article 198 (f) – Innovation Action                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Indicative EU budget                                  | EUR 220 million.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Legal and financial set-up of<br>the Grant Agreements | The rules are described in General Annex G of Horizon Europe Work Programme 2025 <sup>5</sup> . The following exceptions apply:  Beneficiaries may provide financial support to third parties. The support to third parties can only be provided in the form of grants. The EUR 60 000 threshold provided for in Article 207(a) of the Financial Regulation No 2024/2509 does not apply in order to be able to achieve the objectives of this action. The maximum amount of FSTP to be granted to an individual third party is EUR 8.1 million. |  |

| Mode                                                  | One stage, with submission of Full Project Proposal (FPP) FSTP recipients co-funded with NFA                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Invitation date                                       | 03 December 2025                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Deadline FPP                                          | 14 January 2026                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

#### 2.1.3.1 Context

\_

The Chips Act underscores the strategic importance of fostering the growth of chip design activities in Europe to enhance the competitiveness of the Union's semiconductor industry. Pillar I of the Chips Act, the Chips for Europe Initiative, outlines an ambitious plan to strengthen the Union's resilience in semiconductor technologies, also by promoting the growth of fabless startups. These fabless startups are key drivers of innovation, playing a crucial role in key sectors such as AI, telecommunications, and automotive.

<sup>5 &</sup>lt;a href="https://ec.europa.eu/info/funding-tenders/opportunities/docs/2021-2027/horizon/wp-call/2025/wp-14-general-annexes\_horizon-2025\_en.pdf">https://ec.europa.eu/info/funding-tenders/opportunities/docs/2021-2027/horizon/wp-call/2025/wp-14-general-annexes\_horizon-2025\_en.pdf</a>

As fabless companies continue to drive growth in the semiconductor industry, the European share of global fabless semiconductor companies' revenues has shrunk to critically low levels. This highlights the urgent need for strategic initiatives to bolster this sector and enhance Europe's competitiveness. A critical mass of fabless companies is also key to generate further demand that would justify increased investment in semiconductor manufacturing capacity in Europe.

Currently, fabless start-ups can already find support in initiatives such as the Chips Fund, the Strategic Technologies for Europe Platform (STEP) programme, competence centres, and pilot lines. However, there is a crucial gap at the very early stages of these companies which the Design Platform seeks to address.

The Design Platform is at the heart of the Chips for Europe Initiative. It is a key instrument to foster the development of a strong design ecosystem in the Union by creating a pipeline of highly innovative European fabless companies. A key goal of the Design Platform is to support the growth of fabless companies by providing access to funding, foundries, design tools, IP and computing resources.

A consortium to manage the Design Platform, referred to as the Platform Coordination Team (PCT) was selected following a Call for Expression of Interest in Appendix 4 of the Chips Joint Undertaking Multiannual Work Programme 2023-2027. The same consortium was selected following a Call for Proposals for a Coordination and Support Action under Digital Europe in the aforementioned work programme. To ensure the overall coherence of the Platform, to give users a single point of contact, and considering its technical expertise, the consortium is expected to manage a start-up and SME support programme for early stage companies.

This action aims to add a particular aspect to the aforementioned support programme, the disbursement of grants, as well as potentially additional acceleration, incubation and other support activities catered to selected FSTP recipients.

## 2.1.3.2 Scope

Amongst others, the beneficiaries will be responsible for organising and implementing FSTP calls and their evaluations, administering the disbursement of grants and for additional support activities.

This programme will address a key gap in the support of early-stage start-ups and SMEs prior to commercialisation of their innovation. Supported third parties are expected to present innovative chip design projects with a clear perspective towards commercialisation. The programme will facilitate the scaling up of start-ups and SMEs engaged in chip design through FSTP grants.

The beneficiaries will collaborate with the providers of incubation and acceleration services that are funded via a Digital Europe grant for a Coordination and Support Action. The supported third parties will benefit from FSTP grants as well as incubation and acceleration services. In addition, the beneficiaries of this topic will work together with Design Enablement

Teams, who will provide dedicated application engineering support to users from setting up their design environment and design flows up to tape-outs.

## Selections and Evaluation procedure to be run by the beneficiaries

Selections should be made by the beneficiaries with the assistance of a pool of independent experts that evaluate the proposals. Experts should be professionals from the field of semiconductor design or manufacturing and should have an understanding of both the technology and the semiconductor industry.

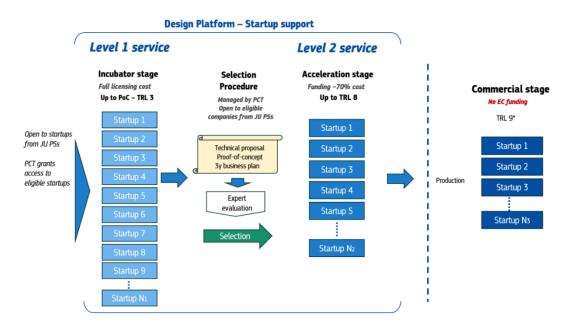

The criteria for giving the financial support for FSTP Level 1 must include the capacity of the applying third party to realise a proof-of-concept design, level of innovation, and EU added value. Beneficiaries are expected to further elaborate on these criteria.

The criteria for giving the financial support for FSTP Level 2 must include the quality of the business case, market viability of possible final products, the quality of the proof-of-concept demonstrator and designs, level of innovation, and EU added value. Beneficiaries are expected to further elaborate on these criteria.

The beneficiaries should establish a quick selection procedure to verify the eligibility of the third party and the capacity of the applying third party to realise a proof-of-concept design or a proof-of-concept demonstrator.

## **Scope for FSTP Level 1**

The following applies to the selection of third parties receiving Level 1 services:

- Third parties should be invited to submit proposals for Level 1 services via a continuous application process with a number of cut-off dates determined by the consortium. There should be at least 2 cut-off dates per year during the continuous application period.

- Selected third parties must design the majority of their chips in-house, in the country of establishment.

- The maximum amount of financial support for Level 1 services should not exceed EUR 100 000 for each third party. A third party may only benefit from Level 1 services once; this includes linked entities.

- The exact amount of the financial support is based on estimates of the eligible costs given by the applicant and assessed by experts designated by the PCT. The funding rate will be up to 100%. Funding may be awarded in the form of lump sums. Funding is paid out based on reaching well-defined milestones. Prefinancing may be awarded as well.

## Financial support for FSTP Level 1

Via FSTP calls, selected startups and SMEs may receive a grant covering certain predetermined eligible costs.

• The financial support is granted to cover:

- Electronic Design Automation (EDA) tool license costs with vendors that have a "General Conditions Agreement" within the context of the Design Platform;

- semiconductor Intellectual Property (IP) blocks licence costs;

- DET services costs and/or costs related to access to computing resources;

## **Scope for FSTP Level 2**

The following applies to the selection of third parties receiving Level 2 services:

- Third parties are invited to submit proposals for Level 2 services via a continuous application process with a number of cut-off dates determined by the consortium. There should be at least 2 cut-off dates per year during the continuous application period.

- Selected third parties must design the majority of their chips in-house, in the country of establishment.

- The maximum amount of financial support for Level 2 services should not exceed EUR 8 000 000 for each third party. A third party may only benefit from Level 2 services once; this includes linked entities.

- The exact amount of the financial support is based on estimates of the eligible costs given by the applicant and assessed by experts designated by the PCT. The funding rate will be up to 35% Union funding, and may be complemented up to 70% by national and/or Union funding. Funding may be awarded in the form of lump sums. Funding is paid out based on reaching well-defined milestones. Prefinancing may be awarded as well.

## Financial support for FSTP Level 2

Via FSTP calls, selected startups and SMEs may receive a grant covering certain predetermined eligible costs.

Start-ups and SMEs in Level 2 may benefit from two main funding streams, provided from the Union's contribution and the Participating States' contribution.

- The financial support is granted to cover:

- Electronic Design Automation (EDA) tool license costs with vendors that have a "General Conditions Agreement" within the context of the Design Platform;

- semiconductor Intellectual Property (IP) blocks licence costs;

- DET services costs and/or costs related to access to computing resources;

- fabrication costs for prototyping.

<sup>&</sup>lt;sup>6</sup> Prior use of Level 1 services is not a prerequisite for eligibility to apply for Level 2 services.

## Admissibility for applications for FSTP

- Third parties should submit applications in a format defined by the PCT consortium. The complexity and length of the applications should be proportionate to the size of the grant.

- Proposals by third parties responding to FSTP calls should include:

- a description and justification by the third party of the proposed costs;

- evidence of the third party's financial capacity to carry out the proposed project, considering that a certain part of overall costs may need to be financed by the third party;

- a description of the project as well as the professional experience of the third party;

## Eligibility for start-ups and SMEs applying for FSTP

All organisations that are eligible for funding in Horizon Europe are eligible for funding in the FSTP calls organised by the beneficiaries. Recipients of FSTP grants will be granted access to the Design Platform<sup>7</sup>.

For further conditions on financial support to third parties, proposers are referred to the Horizon Europe General Annexes<sup>8</sup>.

In addition to eligibility to participate, for the partners of a Participating State that coordinates grants, specific rules may apply regarding the eligibility to national funding.

## 2.1.3.3 Expected outcomes.

A main element of the Design Platform is a **start-up and SME incubation and acceleration programme** that is broadly based on two levels of support as seen in Figure 1.

This programme relies on the cloud service infrastructure managed by the PCT and procured by the Chips Joint Undertaking, as well as services provided by both the PCT and the Design Enablement Teams (DETs) following calls DIGITAL-Chips-2024-CSA-CDP-1 and DIGITAL-JU-Chips-2025-CSA-DET respectively.

Within the context of this action, Level 1 services correspond to an incubation programme and Level 2 services correspond to an acceleration programme.

<sup>&</sup>lt;sup>7</sup> It should be noted that previous work programmes (in particular, Annex 4 of the Chips JU's multi-annual work programme) provided other statements about access to the Design Platform. This has been corrected in the current work programme and in the access conditions specified in the Hosting Agreement, i.e., the formal agreement between the PCT consortium and the Chips JU that defines how the Design Platform is to be managed. It is therefore necessary to clarify here that recipients of FSTP grants will have access to the Design Platform and that all organisations eligible for Horizon Europe funding are also eligible for financial support under the FSTP calls of this topic.

<sup>8</sup> https://ec.europa.eu/info/funding-tenders/opportunities/docs/2021-2027/horizon/wp-call/2025/wp-14-general-annexes horizon-2025 en.pdf

<sup>9</sup> As set out in Annexes 4 and 6 of the Chips Joint Undertaking's multi-annual work programme 2023-2027

*Figure 1 – Design Platform start-up and SME support programme*

Beneficiaries need to ensure that Level 1 support is widely promoted and accessible to fabless European start-ups and SMEs. Here users will be given access to *proof-of-concept* licenses, IP and services that are usually subject to nominal fees. These fees will be partly financed via this action through grants to third parties. Level 1 support is primarily aimed at spinouts and early-stage start-ups.

Start-ups and SMEs at a more advanced stage of development may apply to a selection process to qualify for the Level 2 programme, which offers funding to cover up to 70% of the eligible costs for the selected companies. It is expected that the EU contribution provided via the PCT consortium plus national funding will cover up to 70% of eligible costs. It is expected that in the typical case the JU funding rate is up to 35%. The FSTP calls, including EU funding rates, should be discussed with the Chips JU before the opening of new and revised FSTP calls <sup>10</sup>. Here, EDA and IP license costs and/or conditions should be subject to a "General Conditions Agreement" or MoU agreed to by the Chips Joint Undertaking and made available to the Platform Coordination Team for users of the Design Platform.

Beneficiaries should ensure effective coordination with services and support activities for startups and SMEs financed by the Union outside of this action, particularly through the Coordination and Support Action (CSA) grant awarded to the DECIDE consortium acting as the Platform Coordination Team<sup>11</sup>, to ensure that FSTP grantees are systematically monitored and supported.

<sup>&</sup>lt;sup>10</sup> For administrative purposes, the maximum EU funding rate is considered to be 100%.

<sup>&</sup>lt;sup>11</sup> Following a Call for Proposals in Annex 4 of the Chips Joint Undertaking's multi-annual work programme 2023-2027

The beneficiaries should demonstrate in their proposal the capacity to effectively organise and implement FSTP calls and their evaluations, to disburse grants to startups and SMEs, to assess performance of FSTP recipients, and to track progress over time.

Out of the total amount of EUR 220 million EU funding, the consortium is expected to commit at least 98% on financial support to third parties. At most 2% should be reserved to organise, evaluate, and manage FSTP calls, including awarding and monitoring and reviewing the execution of activities of FSTP recipients, and to execute other support activities. Incubation and acceleration services in addition to those funded via the Digital Europe grant for a Coordination and Support Action (CSA)<sup>12</sup> may be covered as well, if duly justified. Other activities, where deemed necessary for achieving the objectives of the topic, may be proposed as well. Support activities proposed need to be clearly delineated from those covered elsewhere.

Concretely, the following outcomes are expected:

- an effective and efficient start-up and SME support programme;

- a pipeline of sustainable fabless companies that have gone through an acceleration phase.

## 2.1.3.4 Admissibility

Admissibility conditions are described in Annex 1 "HORIZON Europe conditions applicable to Chips JU" of the WP General Annexes.

Regarding page limits:

ChapterFPP PhaseExcellence60 pagesImpact100 pagesQuality and efficiency of the<br/>Implementation100 pages

Proposals with more pages are admissible and will be evaluated but the pages in excess of those maxima will not be considered for the evaluation.

$<sup>^{12}</sup>$  DIGITAL-Chips-2024-CSA-CDP-1 in Annex 4 of the Chips Joint Undertaking's multi-annual work programme 2023-2027

## 2.1.3.5 Eligibility

Eligibility conditions are described in Annex 1 "HORIZON Europe conditions applicable to Chips JU" of the WP General Annexes.

## **Specific eligibility conditions (JU Grant):**

## Use of Article 198(f) of the Financial Regulation

Pursuant to Article 198(f) of the Financial Regulation, a grant may be awarded without a call for proposals for activities with specific characteristics that require a particular type of body on account of its technical competence, high degree of specialisation, or administrative powers, provided that the activities concerned do not fall within the scope of a call for proposals.

The DECIDE consortium acting as the Platform Coordination Team (PCT) and Hosting Consortium of the Design Platform following:

- a Call for Expression of Interest and a Digital Europe Call for Proposals in Appendix

4 of the Chips Joint Undertaking multiannual work programme 2023-2027 (REF: Chips-2024-CDP);

- evaluations by the Chips Joint Undertaking with the support of independent, suitably qualified experts; and

- selection and funding decisions by the Public Authorities Board of the Chips Joint Undertaking on the basis of a ranking list provided by independent experts;<sup>13</sup>

is deemed as the appropriate body to pursue this action in line with Article 198(f) of the Financial Regulation by fulfilling all the conditions required for the application of this provision, as set out below:

- The selected PCT consortium, *DECIDE*, is responsible for operating and coordinating all aspects of the Design Platform. This includes user onboarding and support, operation of the central cloud infrastructure, coordination of related design enablement services, and the implementation of mentoring, incubation, and acceleration programmes for start-ups and SMEs.

- Financial support to selected third parties, particularly start-ups and SMEs, making use of the Design Platform, as envisaged in this action, is a core feature of the Design Platform. Financial support for access to tools, IP, design enablement services and access to prototyping services is key to ensure that third parties can exploit the benefits provided by the deployed infrastructure.

- Annex C of the work programme<sup>14</sup> explicitly mandates that the selected "PCT consortium shall be in charge of running a start-up incubation programme and a start-up acceleration programme in collaboration with the selected DETs". Furthermore, the action corresponds to Phase 4 of the Design Platform's development, as outlined in

<sup>&</sup>lt;sup>13</sup> Decision PAB 2024.56

<sup>&</sup>lt;sup>14</sup> Appendix 4 Chips Joint Undertaking Multiannual Work Programme 2023-2027

Section 4.1.3 of the call for proposals REF Chips-2024-CDP-1,<sup>15</sup> under which the PCT consortium was selected. Section 4.1.3.2 of the call text explicitly makes clear that this phase involves providing support to start-ups and SMEs, complemented by contributions from Participating States.

- Due to the integrated nature of the Platform, this action requires tight coupling with the already ongoing activities of the PCT, financed through Chips-2024-CDP-1. Indeed, this action demands intricate knowledge of the Platform's architecture and user base, the ability to manage sensitive contractual arrangements with Electronic Design Automation (EDA) tool vendors negotiated by the PCT, and needs to be tightly coupled with the delivery of tailored support services to start-ups and SMEs. Via the PCT, start-ups and SMEs will have a single-point-of-contact for all services and support stemming from the Design Platform. Therefore, it would be inefficient for such activities to be executed by an entity independent of the PCT consortium.

- In addition, the DECIDE consortium will run a mentoring programme and already has the technical and organisational capacity to implement acceleration and incubation activities. Therefore, given that the DECIDE consortium is already funded via a grant to implement acceleration and incubation activities for all startups and SMEs, it is best placed to manage the complementary financial support to third parties participating in incubation and acceleration activities, as well as potentially additional acceleration, incubation and other support activities catered to selected FSTP recipients.

Furthermore, the activities covered by this invitation to submit a proposal represent a direct complement of work already entrusted to the PCT through a competitive procedure. This action is essential to the ongoing development and stability of the Design Platform. It is in line with Article 198(f) of the Financial Regulation and it is not within the scope of a call for proposals.

The PCT consortium is composed of the following legal entities:

- 1. INTERUNIVERSITAIR MICRO-ELECTRONICA CENTRUM (IMEC), PIC 999981149, established in KAPELDREEF 75, LEUVEN 3001, Belgium, acting as the coordinator;

- 2. COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES(CEA), PIC 999992401, established in RUE LEBLANC 25, PARIS 15 75015, France;

- 3. FRAUNHOFER GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTENFORSCHUNG EV (FHG), PIC 999984059, established in HANSASTRASSE 27C, MUNCHEN80686, Germany;

- 4. IHP GMBH LEIBNIZ INSTITUTE FOR HIGH PERFORMANCEMICROELECTRONICS (IHP), PIC 999606438, established in IM TECHNOLOGIEPARK 25,FRANKFURT ODER 15236, Germany;

- 5. SILICON AUSTRIA LABS GMBH (SAL), PIC 901837907, established in SANDGASSE 34,GRAZ 8010, Austria;

٠

<sup>15</sup> Idem

- CENTRO **ITALIANO** PER IL **DESIGN CIRCUITI** DEI **INTEGRATI** ASEMICONDUTTORE **PIC** (CHIPS-IT), 878999548, established in VIA SANT'ENNODIO 26, PAVIA 27100, Italy;

- 7. AGENCIA ESTATAL CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS(CSIC), PIC 999991722, established in CALLE SERRANO 117, MADRID 28006, Spain;

- 8. INTERNATIONAL IBERIAN NANOTECHNOLOGY LABORATORY (INL), PIC988145985, established in AVENIDA MESTRE JOSE VEIGA, BRAGA 4715-330, Portugal;

- 9. TECHNISCHE UNIVERSITEIT EINDHOVEN (TU/e), PIC 999977269, established in GROENE LOPER 3, EINDHOVEN 5612 AE, Netherlands;

- 10. TAMPEREEN KORKEAKOULUSAATIO SR (TAU), PIC 902999288, established in KALEVANTIE 4, TAMPERE 33100, Finland;

- 11. 11. CESKE VYSOKE UCENI TECHNICKE V PRAZE (CVUT), PIC 999848744, established in JUGOSLAVSKYCH PARTYZANU 1580/3, PRAHA 160 00, Czechia:

- 12. AKADEMIA GORNICZO-HUTNICZA IM. STANISLAWA STASZICA W KRAKOWIE(AGH), PIC 999844573, established in AL ADAMA MICKIEWICZA 30, KRAKOW 30-059, Poland;

A sub-set of the PCT consortium with selected legal entities from the ones above-mentioned may also be eligible for this call.

## 2.1.3.6 Financial and operational capacity and exclusion

Financial and operation capacity and exclusion conditions are described in Annex 1 "HORIZON Europe conditions applicable to Chips JU" of the WP General Annexes.

## 2.1.3.7 Evaluation procedure

Please refer to the Governing Board Decision on the evaluation and selection procedures related to the calls launched by the Chips JU.<sup>16</sup>

#### 2.1.3.8 Award criteria

Award criteria are described in Annex 1 "HORIZON Europe conditions applicable to Chips JU" of the WP General Annexes.

For more details, please refer to the Governing Board Decision on the evaluation and selection procedures related to the calls launched by the Chips JU. <sup>17</sup>

-

<sup>&</sup>lt;sup>16</sup> Decision GB 2024.71

<sup>&</sup>lt;sup>17</sup> Idem

#### 2.1.3.9 Scores

The scores will be given with a resolution of one decimal.

| Criteria       | Range | Weight (**) | Threshold (*) |

|----------------|-------|-------------|---------------|

| Relevance      | 0-5   | 1.0         | 3             |

| Implementation | 0-5   | 1.0         | 3             |

| Impact         | 0-5   | 1.0         | 3             |

| Total          | 0-15  |             | 10            |

<sup>(\*)</sup> threshold applies to unweighted score.

This is not related to anything. There are no such % in the FSTP or in the SUP

## 2.1.3.10 Reimbursement rate for establishing the EU contribution

Reimbursement rates as percentages of the eligible cost according to HE.

| Type of beneficiary                    | Maximum EU Contribution as % of<br>the Eligible Cost according to HE (*) |

|----------------------------------------|--------------------------------------------------------------------------|

| For profit organization but not an SME | 70 %                                                                     |

| SME (for profit SME)                   | 70 %                                                                     |

| University/Other (not for profit)      | 100 %                                                                    |

<sup>(\*)</sup> beneficiaries may ask for a lower contribution.

On the maximum amount of financial support in line with Article 207(a) of the Financial Regulation

To achieve the objectives of this action, namely to provide start-ups and SMEs access to foundries, design tools, IP and computing resources, in line with the aims set out by the Chips Act, the maximum amount of financial support that can be paid to a third party must exceed the EUR 60.000 threshold set out in Article 207(a) of the Financial Regulation.

The nature of the costs related to the provision of Electronic Design Automation (EDA) tool licenses, IP licenses, foundry costs, computing resources and design enablement services, inherently surpass the threshold. As such, the objective of this action would be impossible to achieve without exceeding it.

<sup>(\*\*)</sup> the weight is only used to establish the ranking of the proposals.

Therefore, in accordance with paragraph 3 of Article 207(a) the threshold is exceeded and set at EUR 8.100.000.

## 2.1.4 Open-source EDA tools development

Topic: HORIZON-JU-Chips-2025-IA-EDA

| Type of Action                       | Innovation Action (IA)                                                                                                                                                                                                                                       |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Indicative EU budget                 | 20 M€                                                                                                                                                                                                                                                        |

| Expected EU contribution per project | The Chips JU estimates that an EU contribution of between EUR 6 and 7 million per project would allow these outcomes to be addressed appropriately. Nonetheless, this does not preclude submission and selection of a proposal requesting different amounts. |

| Mode                                 | Two stage Call, with submission of<br>Project Outline (PO) and Full Project<br>Proposal (FPP)                                                                                                                                                                |

| Call launch date                     | 04 March 2025                                                                                                                                                                                                                                                |

| Deadline PO                          | 29 Apr 2025 at 17:00 Brussels Time                                                                                                                                                                                                                           |

| Deadline FPP Phase                   | 17 Sep 2025 at 17:00 Brussels Time                                                                                                                                                                                                                           |

#### **2.1.4.1** Context

A key objective of the Chips Act under the Chips for Europe Initiative is the 'building up of advanced design capacity for integrated semiconductor technologies'. To this end as part of operational objective 1 of the Chips Act, the Initiative should integrate 'new design facilities with extended libraries and electronic design automation (EDA) tools' into a virtual design platform. As part of a broader suite of resources, the Design Platform will make available a number of open-source tools.

Chip design is a vital element in the semiconductor value chain and open-source Electronic Design Automation (EDA) tools can be key drivers for innovation in this sector by enabling researchers and developers to experiment with new algorithms, architectures, and methodologies.

Access to EDA software, essential for chip development, has traditionally been both heavily restricted and prohibitively expensive, creating significant barriers for start-ups and small-to-medium-sized enterprises (SMEs). Open-source EDA tools can empower start-ups and SMEs with cost-efficient alternatives to expensive commercial licenses, allowing SMEs to

experiment with chip design. This is particularly crucial for SMEs operating in low- to mid-volume production.

Moreover, Europe is facing a considerable workforce shortage in this sector. This requires the cultivation of an open ecosystem to attract and develop more designers and developers. Open-source EDA tools lower the barrier of entry to chip design and thus attract new engineers and chip designers. Students and new entrants in the field can experiment with chip design without limitations on exploitation of their design or restrictive non-disclosure agreements (NDAs), fostering learning and experimentation. Therefore, wide-spread dissemination of these tools can help in addressing the skills gap in the semiconductor industry.

Existing open-source toolchains already support complete chip designs in several mature nodes, which are the technology of choice in a number of applications in fields such as radar design, automotive, aeronautics and space, medical technology, and electronics for harsh environments—industries with a strong European market presence. With relatively low tapeout costs, these nodes present minimal barriers for SMEs, and open-source tools could enable a wide array of European companies and start-ups to enter the chip design arena.

The growing accessibility of low-cost computing resources has opened the door for large-scale exploitation of parallel computing in EDA. However, this potential is often constrained by licensing costs, which limit the number of parallel runs needed for comprehensive adoption. This is an area where open-source implementations can be an interesting proposition. The ability to fully leverage computational resources for unrestricted parallel scaling—especially with the integration of modern machine learning technologies—has become a focal point of interest for many organisations seeking to push the boundaries of innovation.

Therefore, it is expected that over time, open-source EDA tools will offer significant benefits across other areas of chip design, including advanced nodes and highly integrated digital circuits, fostering growth and enhancing efficiency across the entire electronics sector.

The Horizon Europe *Go-IT* project<sup>18</sup> and the FOSSI Foundation have developed a roadmap for open-source hardware. This roadmap should be considered in proposals answering to this call.<sup>19</sup>

Proposals should, where relevant, build upon existing open-source resources and focus on advancing these tools to the next level. Efforts should include bridging the gap between open-source and commercial EDA tools - proposals should include a realistic outline with expectations and objectives to achieve this goal. Overall, proposals should include effective strategies for enhancing existing tools and improve user experience while driving innovation by introducing novel tools and methodologies. Where appropriate, machine learning techniques to improve performance and productivity should be considered.

<sup>&</sup>lt;sup>18</sup> Go IT! | GOIT | Project | Fact sheet | HORIZON | CORDIS | European Commission

<sup>&</sup>lt;sup>19</sup> Roadmap and Recommendations for Open Source EDA in Europe

Technology Readiness Level: Targeted TRL at the end of projects is between 7 and 8.

## 2.1.4.2 Scope

Each proposal must address only one of the following three streams: (i) digital SoC design; (ii) analogue and mixed-signal design; or (iii) productivity, interoperability, and verification. Only one project per stream will be selected.

## (i) <u>Digital SoC design</u>

Modern integrated circuit (IC) design thrives on digital workflows and advanced design automation tools, enabling engineers to capitalise on the increasing circuit density achieved with each new technology node. The exponential progress driven by Moore's Law not only fuels innovation at the industry's forefront but also broadens accessibility across the technological landscape, including at more mature nodes. While much attention is given to cutting-edge design nodes, the enhanced productivity these advancements bring also empowers SMEs, even those with limited design expertise, to undertake projects previously beyond their reach. This democratisation of IC design opens up new markets, fosters innovation, and drives growth across the sector.

Digital chip design serves as the backbone for developing processors, memory, and logic components that power a vast array of electronic devices—from smartphones and computers to IoT systems and cutting-edge AI hardware. Currently, open-source EDA tools for digital design provide sufficient support for mature technology nodes. However, advancing to more sophisticated nodes requires refining existing tools and expanding their functionality. As technology nodes become smaller, the impact of parasitic effects on overall performance—both in terms of power and timing—grows significantly. Continued development is essential to accurately model and mitigate these effects.

## (ii) Analogue and mixed-signal design

For stable, mature nodes, the availability of open-source Process Design Kits (PDKs) and comprehensive open-source design flows already provides significant opportunities for analogue and mixed-signal integrated circuit (IC) design. These tools are particularly valuable for education and training, enabling students, researchers, and engineers to gain hands-on experience in designing, manufacturing, and testing custom analogue and mixed-signal chips. By lowering the cost and accessibility barriers, these resources play a crucial role in equipping the next generation of designers with practical skills, particularly in fields such as sensors, communication systems, and signal processing.

Looking to the short-to-medium term, the goal is to achieve performance and reliability on par with proprietary tools while expanding the capabilities of open-source EDA solutions. Specific focus will be given to advancing tools and methodologies for complex analogue, radio frequency (RF), and terahertz (THz) designs, as these are essential for emerging technologies such as IoT, 5G/6G, and advanced communication systems. By prioritising analogue and

mixed-signal functionality from the outset, open-source EDA tools can drive innovation and expand access for this key segment of Europe's semiconductor ecosystem.

#### (iii) Productivity, interoperability, and verification

Addressing the challenge of labour shortages requires targeted measures to enhance efficiency and accessibility in chip design. In the short term, further developing and leveraging open-source tools can significantly boost productivity by reducing barriers to entry for engineers and designers.

In the short-to-medium term, focusing on improving interoperability between various Electronic Design Automation (EDA) tools will be crucial. Seamlessly integrating open-source EDA tools into established design workflows will enable smoother collaboration between diverse teams and disciplines. This interoperability will reduce time-consuming inefficiencies caused by incompatible systems, streamlining the design process from conceptualisation to final tape-out. For SMEs, in particular, this integration will lower technical barriers, making advanced chip design more accessible and cost-effective.

Furthermore, investing in open-source design verification tools will deliver benefits to the entire chip design industry. Fast and efficient verification solutions with minimal access barriers are essential for accelerating time-to-market and fostering wider adoption. In the medium term, the development of innovative verification methodologies will further enhance efficiency, streamline design processes, and attract skilled talent from diverse disciplines, addressing the industry's growing demand for expertise.